2장. 실습 1/단계 3: 고위합성 (High-Level Synthesis)

HLS를 이용하여 C 설계를 RTL로 합성 해내고 그 결과물을 평가해 본다.

1. 플로우 탐색창에서 'C Synthesis'를 클릭 하여 고위합성을 실시한다. 이어서 합성 결과를 검토한다.

고위합성이 완료되면 합성 가능한 RTL 수준의 HDL(Hardware Description Language) Verilog와 VHDL을 생성하고 정보창에 결과 보고서를 보여준다. 결과 보고서는 요약본(Summary)과 상세본(Detail)이 있다.

2. 합성된 RTL 설계물의 성능 예측(Performance estimate)을 보기 위해 요약본(Summary)을 열어보자. 합성된 RTL의 성능은 클럭의 주기(동작 속도)와 면적(하드웨어의 량)으로 평가 된다. RTL 단계에서 성능은 실제로 반도체 위에 배치와 배선이 이루어지기 전 이므로 예측된 평가(estimate) 라고 한다.

실제로 반도체 평면에 회로의 배치와 배선(Place & Route)을 마치면 지연이 있게 된다. 따라서 안전한 레지스터 간 전송을 위해 클럭의 주기 시간 간격을 늘려야 한다. 아울러 회로가 차지하는 반도체 평면도 증가한다. 따라서 고위합성의 결과로 보여주는 성능은 예측치가 된다.

성능예측 보고서의 요약본은 다음과 같은 항목들을 포함한다.

- 시간 예측(Timing Estimation): 합성기에 가해지는 가장 중요한 조건(constraint)이다. 물리적 지연시간을 의미한다.

합성기는 주어진 지연 목표치(target)에서 불안정 구간(uncertainty)을 뺀 시간을 조합회로의 합성 지연 조건으로 삼는다. 위의 예는 합성의 목표(target)를 10ns 으로 주었다. 향후 배치와 배선(Place & Route)을 위해 여유시간을 2.7ns 로 잡았다. 이 여유시간은 별도 값을 주지 않을 경우 합성기가 목표로 하는 FPGA의 기술 문서에 근거하여 잡는다. [자일링스의 문서상으로 주기의 12.5%로 나와 있으나 그보다 크게 잡는다.] 위의 예는 10.00ns 에서 2.7ns 를 뺀 7.3ns 가 레지스터 사이의 조합 회로에 허용되는 지연조건이 된다. 합성 후 예측된 지연은 6.912ns로 조건 범위내에 있다.

- 성능과 자원 예측(Performance & Resource Estimation):

예측 성능은 레이턴시(latency)와 인터벌(interval)로 평가된다. 레이턴시는 기능을 수행하는데 소요되는 클럭의 갯수다. C 소스에서 for 반복문에 라벨을 Shift_Accum_Loop로 붙여 놓았다. 이 반복문을 수행 하는데 25개의 클럭이 소요되는 것으로 보고 되었다. 함수 fir()을 완료하는데 27개의 클럭을 소모한다. 반복문 탈출에 2개의 클럭이 더 필요했음을 뜻한다. 인터벌(interval)은 설계 모듈이 입력을 받아 계산을 완료하고 출력을 내기까지 소요되는 클럭의 개수다. 예제의 인터벌은 28개다. 레지스터 출력(registered-out)을 위해 1개의 클럭을 더 소모한 것으로 보인다.

자원 예측은 C 설계를 RTL로 구현하면서 사용된 회로의 요소들의 사용량이다. 구현할 목표 하드웨어는 자일링스의 FPGA 다. 자일링스 FPGA의 회로 구성 요소의 단위로는 내장 메모리(BRAM), 곱셈과 누산에 특화된 DSP, 논리식을 구현하는 LUT(Look-Up Table) 그리고 플립플롭 FF 가 있다. C 설계의 for 반목문 내에 곱셈과 덧셈이 DSP 자원으로 구현 됐음을 짐작 할 수 있다. 또한 for 반복문을 풀면서 쉬프트 레지스터를 구현하기 위해 상당량의 FF 가 소요되었다. 그외 for 반복문의 시작과 끝을 제어하기 위한 컨트롤 FSM과 대규모 멀티플렉서 MUX의 구현에 상당량의 LUT 들이 사용되었을 것으로 보인다.

구현된 하드웨어의 구조에 따라 달라지는 레이턴시와 인터벌. 완전한 파이프라인 구조의 하드웨어는 인터벌이 1로 매우 빠른 성능을 보여준다. 실시간 스트림 라인 처리(streamlined processing)에 유리 하지만 엄청난 량의 하드웨어를 필요로 한다. 당연히 전력소모도 많다. 행렬 곱셈처럼 동일한 연산구조를 반복 수행하는 그래픽 처리, 인공지능 분야에 매우 유리한 구조다. 최초 유효 입력 이후 유효 출력이 나오기 시작하기 까지 소요되는 클럭의 개수가 레이턴시다. 성능은 레이턴시 보다 인터벌의 수에 의존한다.

- 하드웨어 인터페이스(HW Interface)

C 에서 고위합성된 RTL 하드웨어가 인접 모듈과 연결되는 입출력 데이터 포트와 컨트롤 포트들을 나열한다. RTL 은 비트폭 및 클럭 상세 수준이다.

하드웨어 모듈이 인접 모듈과 데이터를 주고 받으려면 시스템의 규약에 따른 제어신호가 필요하다. 데이터를 포함해 일련의 제어신호와 절차를 인터페이스(interface)라 한다.

설계의 추상화 수준이 높을 수록 자료 흐름(data flow)에 집중되며 흐름 제어(flow control)는 규약(protocol)으로 정의 되고 겉으로 드러나지 않게 된다. 제어는 하드웨어로 구현될 때 선택이 매우 다양하다. 별도의 제어가 필요없는 고성능 스트림라인(streamlined I/O), 능동(request) 또는 수동(ready) 핸드 쉐이크, 시스템 버스(on-chip bus) 등 적용될 시스템의 규정을 따른다.

C 에서 고위합성된 RTL 설계물은 전자회로로 구현되기 직전의 하드웨어를 기술한 것으로 비트폭(bit-width) 및 클럭(clock) 상세로 기술 되어 있다. 따라서 C의 설계에서 드러나지 않는 핸드 쉐이크용 제어 신호를 가지게 된다. 가장 단순한 메모리 접근에도 두단계 절차가 필요하다. 주소지정이 먼저 선행 되어야 데이터를 읽기 또는 쓸 수 있다.

실제로 C 언어의 배열 변수에 읽기와 쓰기도 한 문장으로 표현 되지만 작동에는 주소 지정이 먼저 있어야 한다. 추상화 수준이 높을 수록 데이터 흐름에 집중하며 실제 작동 절차는 드러나지 않고 규칙되어 있다. 설계자는 높은 추상화 수준에서 문서화 하며 실제 구현은 이 규칙들을 작동절차로 풀어 내는데 바로 컴파일러나 합성기 같은 자동화 도구들이 수행할 몫이다.

합성 보고서의 하드웨어 인터페이스(HW Interface) 항목에는 비트폭 상세 입출력 데이터 및 입출력 제어 신호를 보여준다. 인터페이스 방식을 따로 지시하지 않을 경우 단순 핸드 쉐이크 방식의 규약에 따라 인터페이스를 생성한다.

- 소프트웨어 입출력 정보(SW I/O Information)

C 모델(SW)과 합성된 RTL 모델(HW)의 대응 관계(SW-to-HW Mapping) 관계를 보여 준다. HW 쪽에 제어신호 들이 추가 되었다. 필터 계수 c는 메모리로 구현 되었으므로 데이터 포트 c_q0와 함께c_address0(주소), c_ce0(칩 셀렉트)가 있다. 출력 y에 유효한 값이 실렸다는 표시는 y_ap_vld 로 나타낸다. 인터벌이 1이 아니므로 y 에 유효값이 되는 때를 표시해 주어야 한다.

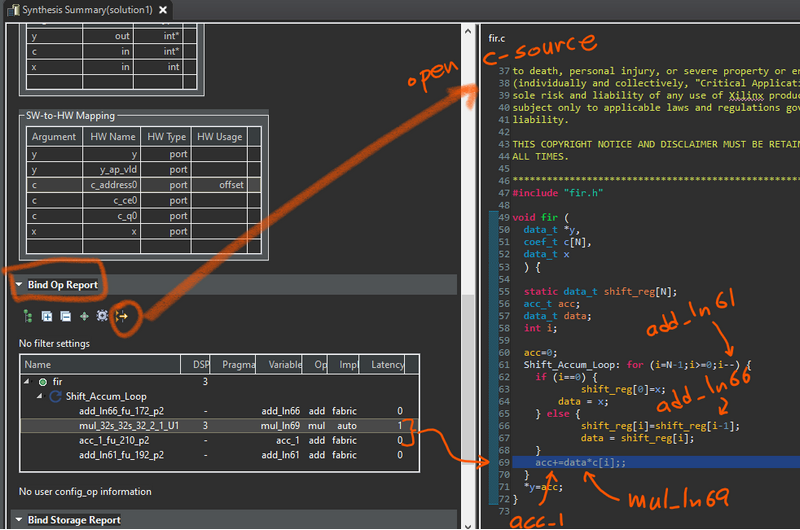

- 연산자 대조표(Bind Op Report)

고위합성 과정에서 C 모델의 연산자가 어떤 하드웨어로 구현 되었는지 보여준다. 32 비트 곱셈기(mul_ln69)와 누산기(acc_1) 그리고 두개의 가산기(add_ln66, add_ln61)가 사용되었다. 두 변수 입력의 32비트 곱셈기와 누산기는 상당한 규모의 하드웨어를 필요로 할 뿐만 아니라 지연도 크다. 연산을 위해 특별히 마련된 DSP 블럭으로 구현되었다. 두개의 가산기는 C 설계의 반복 구문(for-loop)의 1가감산과 쉬프트 레지스터의 인덱스 가감산을 위한 것이다. 증감량이 고정된 상수와 변수 가감산기로 구현되었다. 반복문이 어떻게 풀려(loop un-rolling) 어느정도 규모의 하드웨어가 되었는지 알 수 있다. 이를 확인해 보기 위해 각 연산기가 C 소스의 어느 문장에서 변환되었는지 대조해 볼 수 있는 기능을 제공한다. 향후 최적 합성 결과를 얻기 위한 합성 조건을 세울때 유용하다.

[이 기능에 약간의 오류가 있다. 시뮬레이션 용 테스트 벡터를 자동생성을 위해 중간 C 파일이 생성한다. 이때 C 설계 파일과 동일한 이름을 가진 파일이 생성 되는데, 이 파일을 잘못 불러 온다. 엉뚱한 파일을 불러놓고 연산자와 대조하면 69번줄을 지시하고 있다. 이 문제는 'csim' 폴더를 삭제하면 해결된다. 중간 파일들은 C Simulation을 실시하면 다시 생성된다.]

- 저장소 대조표(Bind Storage Report)

C 설계 소스에 일반적으로 저장이 필요한 변수는 레지스터(플립플롭, FF)로 변환된다. 하지만 배열형이 있을 경우 고위합성기는 고집적 메모리로 변환 한다. 메모리는 고집적 저장 장치로서 실리콘 면적을 줄일 수 있으나 속도가 느리고 주소를 먼저 지정해야 하기 때문에 한개 이상의 레이턴시를 소모한다. 이 예제에서는 쉬프트 레지스터에 32비트 레지스터가 11개가 필요했다. 레이턴시 클럭을 1개 더 사용하더라도 1포트 램(ram_1p)으로 구현되었음을 알 수 있다. 인터벌을 줄이기 위한 최적화 조건을 주면 다른 결과를 얻을 수도 있다.

댓글 없음:

댓글 쓰기